~超大容量・低消費電力・高性能不揮発性メモリ開発を加速~

シリコン半導体デバイスの微細化に伴って増大する消費電力の課題を克服するために、スピントロニクス技術を利用した不揮発性メモリであるスピン移行トルク磁気抵抗メモリ(STT-MRAM)の研究開発が活発に行われています。

東北大学材料科学高等研究所の陣内佛霖助教、電気通信研究所の五十嵐純太博士後期課程学生(日本学術振興会特別研究員)、深見俊輔教授、大野英男教授(現総長)らは、STT-MRAMの主要構成要素である磁気トンネル接合(MTJ)に新しい構造を採用することで、わずか原子10個程度(2.3ナノメートル)の直径を有する世界最小磁気トンネル接合素子を作製し、車載応用に必要とされる高温でのデータ保持特性を維持しながら、DRAMなどのワーキングメモリの置き換えに必要とされる高速低電圧動作を実証しました。本研究により、超大容量・低消費電力・高性能不揮発性メモリ、およびそれを用いた超高性能低消費電力集積回路の開発が加速することが期待されます。

本研究成果は、2020年12月12-18日(米国時間)にオンラインで開催される、半導体素子に関する世界で最も影響力のある技術会議、「米国電子情報学会(IEEE)主催の国際電子デバイス会議(International Electron Devices Meeting)」で発表されます。

シリコン半導体デバイスの微細化に伴って増大する消費電力の課題を解決するために、高速動作が可能な不揮発性メモリであるスピン移行トルク磁気抵抗メモリ(STT-MRAM)の研究開発が活発に行われています。2020年現在、大手半導体メーカーからSTT-MRAMを使用した製品の量産が進められています。これらの製品には、2Xナノメートル世代の製造技術[注1] が用いられており、STT-MRAMのデータの記憶を担う、磁気トンネル接合(MTJ)素子のサイズは、直径数十ナノメートル程度となっています。今後、微細化が進んだ、最先端および次世代の集積回路技術でSTT-MRAMを製造するためには、MTJのさらなる微細化が必要となります。ここで重要となるのが、データ保持特性(熱安定性)を維持しながらデータの書き込み特性を向上することです。

現在量産が進められているSTT-MRAMには、2010年に今回の東北大学の研究グループが開発した、界面磁気異方性を利用するCoFeB/MgO積層構造を有したMTJが用いられています。この構造では、高いMTJのデータ保持特性を得るためにCoFeB/MgO界面における界面磁気異方性を利用していますが、この方式には物理的な限界があり、MTJサイズが20ナノメートルよりも小さくなると、十分なデータ保持特性が維持されないという課題がありました。

この課題を解決するために、同研究グループは、2018年に界面磁気異方性MTJに代わる技術として、磁性層の膜厚をその直径よりも十分に厚くすることで有効に働く形状磁気異方性を活用する、形状磁気異方性MTJを提案しました。ここでは世界最小(当時)3.8ナノメートルの素子の作製とその基本動作実証に成功し、一桁ナノメートル台までの道が切り拓かれました。しかし形状磁気異方性MTJでは、磁性層の膜厚を厚くすることでデータ保持特性を高くできますが、一方その膜厚を厚くし過ぎると素子信頼性が低下してしまうという課題がありました。

今回、同研究グループは、2018年に提案した従来型の形状磁気異方性MTJにおける課題を解決するために、形状磁気異方性に加えて新たに静磁気結合を利用する新しい構造を開発しました。そして直径2.3ナノメートルまでの微細化に成功し、高温でのデータ保持特性や高速低電圧での磁化反転などの従来技術を圧倒する高性能動作を実現しました。この2.3ナノメートルというサイズは、物質中の原子と原子の間隔が約0.2ナノメートルなので、わずか原子10個程度が一方向に並んだ究極の微細スケールであることを意味します。

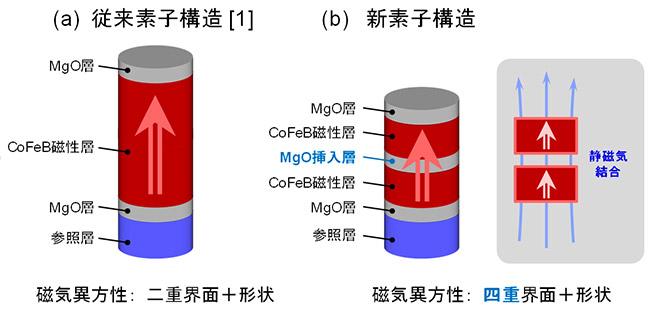

今回作製した構造は、従来型素子[図1(a)]では一層の磁性層が用いられていたのに対して、磁性層にMgO層が新たに挿入されており、形状磁気異方性だけでなく界面磁気異方性を増大させられます。これにより素子のデータ保持特性を維持しながら磁性層膜厚を薄くでき[図1(b)]、素子信頼性を向上できます。この構造を形状磁気異方性MTJに適用するためには、MgO挿入層で隔てられた磁性層の磁化(磁石の向き)が同じ方向を向く(結合する)必要があります。このMgO層の挿入による磁性層間の結合と界面磁気異方性の増大は一般にはトレードオフの関係にありますが、実際にMTJを作製して磁性層同士の結合を評価したところ、MTJサイズを小さくしていくと、古典的電磁気学的な効果である静磁気的な相互作用による結合(静磁気結合)が有効に作用することで、大きな界面磁気異方性と強い磁気結合を両立できることが明らかになりました。

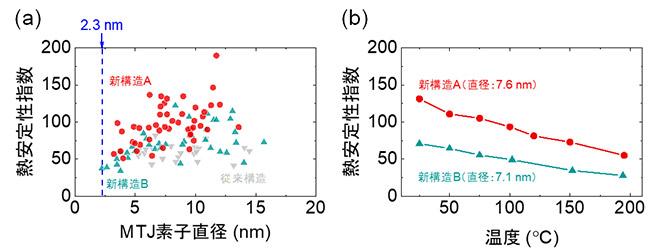

この静磁気結合した積層磁性体を用いた形状磁気異方性MTJ構造を設計し、実際にシリコン基板上に素子を作製しました。素子には現在の量産化が進められているMTJ素子と同じCoFeB/MgO材料が用いられています。東北大学電気通信研究所附属ナノ・スピン実験施設にて成膜および微細加工プロセス条件を精密に制御することによって、低消費電力に必要となる低い抵抗面積積を有し、直径2.3ナノメートルまでの極微細MTJの形成に成功しました[図2(a)]。

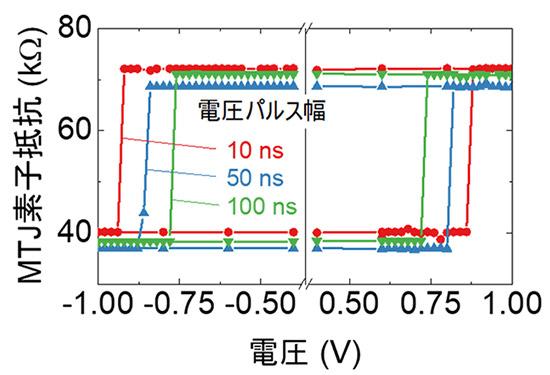

作製した素子特性を評価したところ、データ保持特性の指標となる熱安定指数は、(1)室温にて直径3.5ナノメートルのMTJ素子においても主要なアプリーケーションで必要とされる値である80を満たし[図2(a)]、また(2)車載応用に必要とされる150℃にて直径7.6ナノメートルのMTJ素子において70を上回る[図2(b)]ことが確認されました。情報書き換え特性についても、直径5ナノメートル以下(最小直径3.5ナノメートル)のMTJで、印加電圧1 V以下の電圧パルスによる磁化反転を室温で実現しました。またDRAMなどのワーキングメモリの置き換えに必要となる10ナノ秒での高速動作も直径7.6ナノメートルのMTJで実現されました[図3]。加えて、静磁気結合積層構造を有する形状磁気異方性MTJは、現在量産が進められている界面磁気異方性MTJと比べて、電流による磁化反転の効率が3倍以上高くなることも確認されました。

静磁気結合した積層磁性体を用いた形状磁気異方性MTJには、現在量産されているMTJ素子と同じ材料であるCoFeB/MgO材料が用いられていることから、大手半導体デバイスメーカーの既存設備でもこの新素子構造を製造可能です。また従来の形状磁気異方性MTJでは1つの磁性層膜厚しか制御できなかったのに対して、新構造形状磁気異方性MTJではMgO挿入層の枚数や各CoFeB層の膜厚を個別に制御でき、これにより様々な用途の要求に応じたMTJの設計開発が可能となります。本研究は、半導体集積回路の究極の微細世代までのMTJ技術の微細化指針を示したことになり、超大容量・低消費電力・高性能不揮発性メモリの開発、及び車載応用などの社会実装が加速することが期待されます。

本研究は科学技術振興機構(JST)産学共創プラットフォーム共同研究推進プログラム(OPERA)「世界の知を呼び込むIT・輸送システム融合型エレクトロニクス技術の創出」(領域統括 東北大学 遠藤哲郎)、日本学術振興会(JSPS)科学研究費助成事業(研究代表者 陣内佛霖、五十嵐純太)などの支援により行われました。

図1) (a)従来型形状磁気異方性MTJ素子構造(2018年開発)と、(b)本研究で提案した、静磁気結合を有する積層構造を用いた形状磁気異方性MTJ素子構造の模式図。新素子構造では、界面磁気異方性を増大することによって、薄い磁性層膜厚でも素子の高性能化を実現できる。2つの磁性層は、MgO挿入層を介して静磁気結合によって単一の磁性層のように振る舞う。 [1] K. Watanabe et al., Nature Communications 9, 663 (2018).

図2)本研究で作製した静磁気結合を有する新構造形状磁気異方性MTJ素子と従来型の形状磁気異方性MTJ素子での、室温における熱安定性指数のMTJ素子直径依存性の関係の比較(a)と、一桁ナノメートルの直径を有する新構造形状磁気異方性MTJ素子での熱安定性指数の温度依存性(b)。新構造AとBは、図1(b)のCoFeB磁性層の膜厚がそれぞれ5ナノメートルと7.5ナノメートルである構造を指す。

図3)本研究で作製した静磁気結合を有する新構造形状磁気異方性MTJ素子の電圧パルスによる磁化反転の測定結果。電圧パルス幅が10ナノ秒でも磁化反転している。測定に使用した素子は、新構造B(CoFeB膜厚:5+5ナノメートル)で直径は7.6ナノメートル。

| Title: | “High-Performance Shape-Anisotropy Magnetic Tunnel Junctions down to 2.3 nm” (2.3ナノメートルまでの高性能形状磁気異方性磁気トンネル接合) |

|---|---|

| Authors: | Butsurin Jinnai*, Junta Igarashi*, Kyota Watanabe, Takuya Funatsu, Hideo Sato, Shunsuke Fukami, and Hideo Ohno(*: 共同筆頭著者) |

| Conference: | IEEE International Electron Devices Meeting (IEDM) |

東北大学電気通信研究所

教授 深見 俊輔

| Tel: | 022-217-5555 |

|---|---|

| E-mail: | s-fukami@riec.tohoku.ac.jp |

科学技術振興機構 イノベーション拠点推進部

OPERAグループ

伊藤 哲也

| Tel: | 03-6272-3816 |

|---|---|

| E-mail: | opera@jst.go.jp |

東北大学材料科学高等研究所 広報戦略室

| Tel: | 022-217-6146 |

|---|---|

| E-mail: | aimr-outreach@grp.tohoku.ac.jp |

科学技術振興機構 広報課

| Tel: | 03-5214-8404 |

|---|---|

| E-mail: | jstkoho@jst.go.jp |