~機械学習や組合せ最適化に適した高い演算性能と電力効率が明らかに~

東北大学、カリフォルニア大学サンタバーバラ校(アメリカ)、メッシーナ大学(イタリア)の研究チームは、機械学習や組合せ最適化などの用途で威力を発揮する確率論的(「P」)コンピューターを開発し、優れた演算性能と電力効率を明らかにしました。

人工知能(AI)やデジタルトランスフォーメーション(DX)(注3)の進展に伴いコンピューターに要求される演算性能は飛躍的に増大しており、一方で昨今の社会情勢の中ではコンピューターの省電力化もまた重要な課題です。これら要求の全てを従来型(古典)コンピューターで対応するのは難しく、古典コンピューターが苦手とする問題に特化した新概念コンピューターの研究開発が活発に行われています。

今回研究チームは、機械学習や組合せ最適化などを高速かつ省電力で解く「Pコンピューター」を、自然の熱で状態が確率的に変化する新規スピン素子とプログラム可能半導体回路(Field Programmable Gate Array; FPGA)(注4)を用いて構築し、その性能を評価しました。組合せ最適化を例に、古典コンピューターで確率的アルゴリズムを実行した場合と比較し、Pコンピューターは約5桁高い演算性能と約1桁低い消費電力を実現できることを明らかにしました。

今後本技術を発展させることで、低炭素社会の実現に向け需要が高まっている、エッジで複雑性の高い問題を省電力で処理する情報機器などの実現に繋がるものと期待されます。

本研究成果は、2022年12月3-7日(米国時間)にアメリカで開催される学術会議 「International Electron Devices Meeting: IEDM」で発表されました。

昨今の情報社会は、人工知能(AI)、モノのインターネット(IoT)、デジタルトランスフォーメーション(DX)、ビッグデータなどのキーワードに彩られており、これらを活用した暮らしやすい社会の実現に向けて、コンピューティング技術にはこれまで経験したことがないペースでの演算性能の向上が要求されています。これと同時に、地球温暖化ガスの排出を抑制して2050カーボンニュートラル(注5)を達成するため、コンピューティング技術には省電力化という課題も突き付けられています。この演算性能の向上と省電力化は相反する関係にあり、従来型のコンピューターのみで多様化する社会的要求の全てに対応することは困難です。このため各用途に特化した様々な新概念コンピューターの研究開発が活発に行われています。量子コンピューターはその一例であり、分子軌道の計算など量子力学的性質の取り扱いが本質的に重要となる問題などを効率的に処理できると期待されます。

本研究の対象である「確率論的コンピューター(Pコンピューター)」も特定の用途で威力を発揮すると期待される新概念コンピューターの一つです。量子コンピューターが0状態と1状態の重ね合わせで情報を表現する“量子ビット:Qビット”で構成されるのと同様に、Pコンピューターは、0と1を時々刻々と確率的に出力して情報を表現する“確率ビット:Pビット”で構成されます。古典コンピューターが苦手とする問題の典型例に、膨大な選択肢の中から条件をよく満たす候補を探す問題(組合せ最適化問題)、ある条件下で起こりそうな現象を大量に出力する問題(サンプリング)、複雑なデータの背後にあるルールやパターンを学習する問題(機械学習)などがあります。これらの問題を扱う際には、しばしば確率的なアルゴリズムが用いられますが、情報を0と1で決定論的に表現して逐次的に処理する古典コンピューターとは本質的に相性が悪く、計算に多くの電力を費やすという課題があります。

2019年に東北大学とパデュー大学(アメリカ)の研究チームは、自然の熱で確率的に状態が更新されるスピントロニクス(注6)素子を用いてPビットを構築し、それを用いた「Pコンピューター」の原理実証を行いました(東北大学プレスリリース 『室温動作スピントロニクス素子を用いて量子アニーリングマシンの機能を実現』)。この研究では8個のPビットからなる小規模な原理実証システムが構築され、最大945までの整数の因数分解(945 = 63×15)などが実証されました。また2022年2月には5つのPビットを用いた機械学習の原理実証も報告されています。今後の社会実装に向け、Pコンピューターの規模の拡大と、類似技術に対する性能面での定量的な評価が求められていました。

今回、東北大学の小林奎斗氏(大学院生・工学研究科)、金井駿准教授(電気通信研究所)、大野英男教授(現総長)、深見俊輔教授(電気通信研究所)らは、カリフォルニア大学サンタバーバラ校のKerem Camsari博士、メッシーナ大学のGiovanni Finocchio博士らと共同で、確率動作するスピントロニクス素子と、プログラムが可能な半導体回路(FPGA)を組み合わせ、先行研究から大幅に規模が拡大されたPコンピューターを実現しました。そして組合せ最適化問題のアルゴリズムを用い、52,193,789 = 6,883×7,583をはじめとする、以前の研究を5桁上回る様々な整数の因数分解に成功しました。加えて実験で測定された性能を基に、古典コンピューター上で確率的なアルゴリズムを実行して計算を行う場合と比較して、演算性能は約5桁、消費電力は約1桁低減されるポテンシャルがあることを明らかにしました。

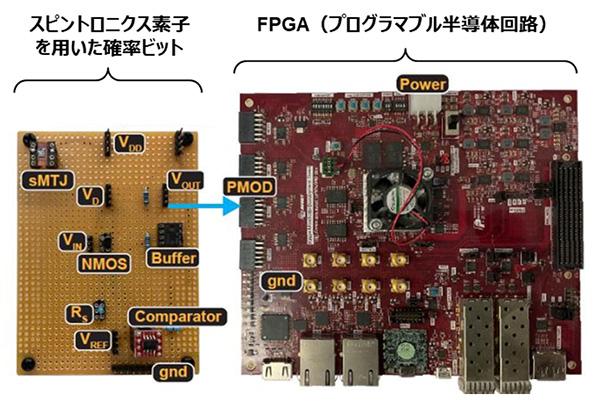

今回の研究のポイントは、確率動作スピントロニクス素子からなる高性能Pビットを、大規模な演算が可能なFPGAと組み合わせた点にあります。図1は作製したシステムの写真です。FPGA上には最大7,085個のPビットを疑似的に実装でき、これを自然な熱によって電力を消費することなく状態が更新されるスピントロニクスPビットで駆動することで、高度な計算が可能となりました。別の言い方をすると、半導体回路上に作製した大量の性能の低い疑似乱数発生器を、スピントロニクス素子の力で性能の高い物理乱数発生器に変え、高度な計算を可能とした、とも言えます。

図1)構築した確率動作スピントロニクス素子からなる確率ビットとFPGAからなる確率論的コンピューター(Pコンピューター)の写真

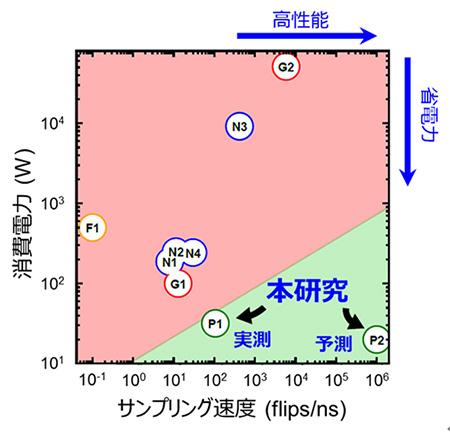

続いて研究チームは、スピントロニクス素子を用いたPコンピューターの演算性能と消費電力を測定し、古典コンピューターで確率的なアルゴリズムを用いて演算を行う場合との比較を行いました。図2にその比較が示されています。横軸はサンプリング速度であり、これはコンピューターの演算性能に相当します。縦軸は消費電力です。FPGAを用いたPコンピューターは実測値ベース(106.28 flips/ns, 32.72 W)で既に古典コンピューターの典型値(図中のG1, N1, N2, N4)と比べて消費電力は1/3から1/10程度低く、演算性能は2倍から10倍程度高いことが分かります。加えて、東北大学のグループは以前に超高速で熱による状態更新が可能なスピントロニクス素子を開発しており(東北大学プレスリリース『スピントロニクス疑似量子ビットを従来比100倍超に高速化』)、また同様なスピントロニクス素子は磁気抵抗メモリ(Magnetoresistive Random Access Memory)において既にメガビット以上の規模で量産されています。図のP2はこれらの技術を適用して専用集積回路を作製した場合に予測される値(1,000,000 flips/ns, 20 W)です。実測値から演算性能はさらに4桁向上、消費電力はさらに約40%低減し、古典コンピューターの典型値を演算性能で約5桁、消費電力で約1桁凌駕する特性が得られることが分かります。

図2)スピントロニクス確率論的(「P」)コンピューターと、古典コンピューターで確率的アルゴリズムを実行した場合の、計算性能(サンプリング速度:横軸)と消費電力(縦軸)の比較。P1は本研究での実測値であり、P2は既に確立されているスピントロニクス素子技術・集積化技術を用いた場合に予測される値。N1~N4はGPU(Graphics Processing Unit)コンピューターを用いた場合、G1~G2はTPU(Tensor Processing Unit)コンピューターを用いた場合、F1はシミュレーテッドアニーリングコンピューターを用いた場合の報告値。

本研究によって、これまで基本動作の確認に留まっていたスピントロニクスPコンピューターが、確率的に取り扱うことで効率的に求解できる問題に対して、古典コンピューターと比べて圧倒的に優れた計算性能と電力効率を示すことが明らかになりました。今後、図2で「P2」としてプロットされた特性を実際に専用集積回路において実現するためには、材料・素子・回路・アーキテクチャ・アルゴリズムの全階層において、いくつかの技術課題に取り組んでいく必要があります。これらの課題に粛々と取り組んでいくことで、まだ誰も見たことのない超高性能・省電力コンピューターが実現される「確率」が高まっていくものと期待されます。

本研究は、科学技術振興機構(JST) 戦略的創造研究推進事業 CREST「スピンエッジコンピューティングハードウェア基盤」(研究代表者:佐藤 茂雄)JPMJCR19K3、および同事業さきがけ「不確定性スピントロニクス素子」(研究代表者:金井 駿)JPMJPR21B2、などの支援を受けて行われたものです。

| Title: | “Experimental evaluation of simulated quantum annealing with MTJ-augmented p-bits” (磁気トンネル接合駆動確率ビットを用いた疑似量子アニーリング) |

|---|---|

| Authors: | Andrea Grimaldi, Kemal Selcuk, Navid Anjum Aadit, Keito Kobayashi, Qixuan Cao, Shuvro Chowdhury, Giovanni Finocchio, Shun Kanai, Hideo Ohno, Shunsuke Fukami and Kerem Y. Camsari |

| Conference: | IEEE International Electron Devices Meeting (IEDM) |

東北大学電気通信研究所

教授 深見 俊輔

| Tel: | 022-217-5555 |

|---|---|

| E-mail: | s-fukami@tohoku.ac.jp |

東北大学電気通信研究所 総務係

| Tel: | 022-217-5420 |

|---|---|

| E-mail: | riec-somu@grp.tohoku.ac.jp |