~直径5ナノメートル以下の磁気トンネル接合素子で高速動作を実証~

DXおよびカーボンニュートラル(脱炭素)社会の実現に必要不可欠な半導体の分野では熾烈な技術競争が行われています。なかでも、スピントロニクス技術を利用した不揮発性メモリであるスピン移行トルク磁気抵抗メモリ(STT-MRAM)並びにそれを混載メモリに適応した省電力ロジックは、半導体集積回路の大幅な低消費電力化をもたらすと期待され、特に注目されています。しかし、将来の微細世代技術に適用して社会実装を促進するためには、記憶素子の微細化と加えて高速動作に関する性能の向上が求められていました。

東北大学材料科学高等研究所の陣内佛霖助教、電気通信研究所の五十嵐純太学術研究員、深見俊輔教授、大野英男教授(現総長)らは、高速書き込み動作を特徴づける時定数を制御できる磁気トンネル接合(MTJ)(STT-MRAMの情報記憶素子)の構造を提案し、5ナノメートル以下の直径を有するMTJ素子で3.5ナノ秒までの高速書き込み動作を実証しました。これは、STT-MRAMが将来のオングストローム世代半導体製造技術[注]でのSRAMや高速DRAMの代替として使えることを示す重要な成果です。本研究により、超大容量・低消費電力・高性能不揮発性メモリ、およびそれを用いた超高性能・低消費電力半導体集積回路の開発が加速することが期待されます。

本研究成果は、2021年12月11-15日(米国時間)に米国サンフランシスコで開催される、半導体素子に関する世界で最も影響力のある学術会議、「米国電子情報学会(IEEE)主催の国際電子デバイス会議(International Electron Devices Meeting)」で発表されました。

昨今の社会的背景から注目を集めている半導体は、DXおよびカーボンニュートラル(脱炭素)社会を実現する上で重要な役割を担っています。現在5ナノメートル世代最先端半導体製造技術による製品がスマートフォンやPCに搭載されています。一方でSRAMやDRAMといった揮発性メモリを、電源を切っても情報が保持される不揮発性メモリで置き換えることで、半導体集積回路のさらなる低消費電力化の実現が可能となります。特にスピントロニクス技術を利用した不揮発性メモリであるスピン移行トルク磁気抵抗メモリ(STT-MRAM)は、Intel、TSMCやSamsungなどの大手半導体デバイスメーカーにより活発に開発が進められ、現時点では22/28ナノメートル世代半導体製造技術で量産・製品化され、14/16ナノメートル世代半導体向けの技術開発も進んでいます。

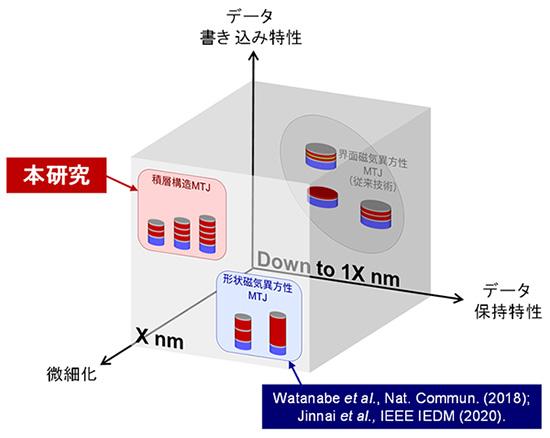

STT-MRAMの情報記憶を担いその性能を決めるのが磁気トンネル接合(MTJ)素子です。MTJ素子は、用途に応じてデータ書き込み・保持特性が設計されます。ひとつは、長期間(10年以上)のデータ保持が可能なフラッシュ代替用途、もうひとつは高速(数ナノ秒)動作が可能なSRAM代替用途です[図1]。また半導体微細化とともにMTJ素子自体の微細化も求められ、最先端の5ナノメートル世代そして将来のオングストローム世代の半導体製造技術には直径10ナノメートル以下の極微細MTJ素子が必要とされています(現在のMTJ素子直径は30ナノメートル以上)。

現在大手半導体デバイスメーカーによって開発が進められているMTJ素子は、2010年に大野英男教授(現総長)が率いる東北大学の研究グループが開発した、CoFeB/MgO界面の垂直磁気異方性を利用したMTJ素子技術が基になっています。しかしこの構造では、MTJ素子の微細化に伴ってデータ保持特性の維持ができないため、直径10ナノメートルを下回る極微細領域でのMTJ素子開発は困難でした。このような背景から同グループは2018年に、情報を記憶する層であるCoFeBの膜厚を直径よりも十分に厚くすることで有効に働く形状磁気異方性を利用したMTJ素子(形状磁気異方性MTJ素子)を提案し、2020年に直径10ナノメートル以下の極微細領域で車載応用にも適用可能な十分に高いデータ保持特性ならびに10ナノ秒までの高速書き込みを実証しました。一方で膜厚が厚い形状磁気異方性MTJ素子では、ラストレベルキャッシュ用SRAMに匹敵する10ナノ秒よりも高速な(数ナノ秒の)データ書き込みの実現が課題として残っていました。

今回、同研究グループは、高速動作を重視した素子構造にすることで、直径5ナノメートル以下のMTJ素子で10ナノ秒以下の高速動作を実現しました。今回開発したMTJ素子の特徴は、2020年提案の形状磁気異方性MTJ素子と補完し合っており、用途に応じてそれぞれのMTJ素子を使い分けることが可能となります[図1]。

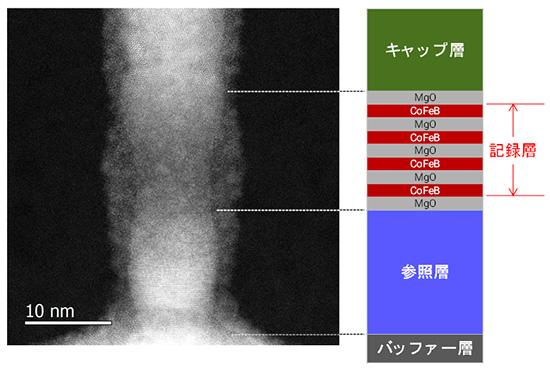

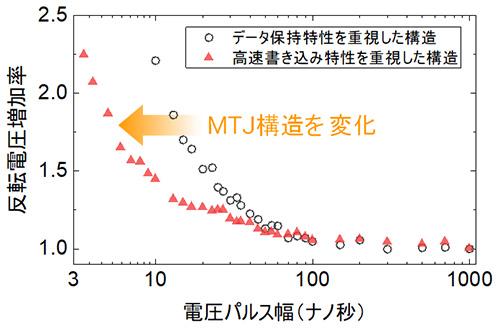

数ナノ秒(歳差)領域の高速磁化反転(データ書き込み)では、熱ゆらぎによる助けなく磁化が反転しなければならず、印加電圧のパルス幅が短くなるほど反転電圧が増加します。この歳差領域での反転電圧増加を抑えるには、高速磁化反転動作を特徴づける時定数である緩和時間を制御する(短くする)ことが必要になります。これには、MTJ素子のCoFeB層の膜厚を薄くしながら磁気異方性を大きくすることが必要になります。これを実現するために、CoFeB/MgO界面の数を増やし界面磁気異方性の寄与を大きくしながらCoFeB層の膜厚を薄くした積層磁性体構造を開発しました[図2]。極微細領域では積層磁性体が、古典的電磁気学的な効果である静磁気的な相互作用により結合しているため、MgO挿入層で隔てられたCoFeB層がひとつの記録層として振る舞うことが同グループの以前の研究から明らかになっています。この構造を適用したMTJ素子を実際に作製したところ、世界最小の直径2.0ナノメートル(20オングストローム)までの極微細MTJ素子の動作を確認しました。またMTJ構造を変化させることで直径5ナノメートル以下のMTJ素子で歳差領域の反転電圧増大を抑制しながら10ナノ秒以下の高速書き込みを実現しました[図3]。これは、STT-MRAMが将来のオングストローム世代の半導体製造技術でもSRAMや比較的高速なDRAMの代替としても使えることを示す重要な成果です。

積層磁性層構造は、極微細領域で静磁気的に磁性層が結合するため、縦方向の膜構造の設計自由度を有します。したがってフラッシュ型やSRAM型STT-MRAMなど用途に応じたMTJ素子構造の設計ができます。また特性制御は現在主流のCoFeB/MgO材料で実現できるため、大手半導体デバイスメーカーの既存設備でもこれらのMTJ構造が製造可能です。本研究により、極微細領域でのMTJ素子技術の設計指針が示され、STT-MRAM基盤技術が確立されました。これは、STT-MRAMが将来のオングストローム世代最先端半導体製造技術で車載応用からIoT/AIまでの幅広い用途への展開が可能であることを示しており、高性能・低消費電力半導体集積回路の社会実装が加速されカーボンニュートラル社会の実現に貢献することが期待されます。

また本研究のMTJ素子のすべての作製工程は、同グループが有する微細加工技術を駆使して、東北大学電気通信研究所附属ナノ・スピン実験施設で行われました。直径一桁ナノメートル極微細MTJ素子の作製に成功している研究機関は世界でも数少なく、世界に先駆けてオングストローム世代半導体製造技術に必要不可欠である極微細MTJ素子技術の研究開発指針を示すことでその技術開発が加速されることが期待されます。

本研究は科学技術振興機構(JST)産学共創プラットフォーム共同研究推進プログラム(OPERA)「世界の知を呼び込むIT・輸送システム融合型エレクトロニクス技術の創出:領域統括 東北大学 遠藤 哲郎」、日本学術振興会(JSPS)科学研究費助成事業などの支援により行われました。

図1)MTJ素子は用途によってデータ書き込み・保持特性の仕様が決まる。同時に、シリコン半導体素子と集積化されるため、MTJ素子の微細化も必須となっている。直径十数ナノメートルまでのMTJ素子技術はすでに量産開発が進められている。直径一桁ナノメートル(5ナノメートル以下)のMTJ素子技術では、東北大グループから車載応用に適用可能な高データ保持性能を有する素子の動作が実証されている[1,2]。本研究は、SRAM置き換えを視野にいれた高速動作可能な直径5ナノメートル以下のMTJ素子を開発した。[1] K. Watanabe et al., Nature Communications 9, 663 (2018). [2] B. Jinnai et al., IEEE IEDM, 24.6.1(2020).

図2)本研究で作製した積層磁性層構造を有するMTJの透過型電子顕微鏡(TEM)像とその膜構造。CoFeB/MgO層を複数回(図では4回)積層することで界面磁気異方性を増大。

図3)高速書き込み特性とデータ保持特性をそれぞれ重視した構造における反転電圧増加率の電圧パルス幅依存性。反転電圧増加率は1マイクロ秒での反転電圧で規格化した反転電圧。構造を変化させることで、直径5ナノメートル以下の素子で電圧パルス幅10ナノ秒以下の歳差領域での反転電圧の増大を抑制。

| Title: | “Fast Switching Down to 3.5 ns in Sub-5-nm Magnetic Tunnel Junctions Achieved by Engineering Relaxation Time” (緩和時間制御によるサブ5ナノメートル磁気トンネル接合での3.5ナノ秒までの高速磁化反転) |

|---|---|

| Authors: | Butsurin Jinnai*, Junta Igarashi*, Takanobu Shinoda, Kyota Watanabe, Shunsuke Fukami, and Hideo Ohno (*: 共同筆頭著者) |

| Conference: | IEEE International Electron Devices Meeting (IEDM) |

東北大学電気通信研究所

教授 深見 俊輔

| Tel: | 022-217-5555 |

|---|---|

| E-mail: | s-fukami@riec.tohoku.ac.jp |

東北大学国際集積エレクトロニクス研究開発センター

センター長・教授 遠藤 哲郎

| Tel: | 022-796-3410 |

|---|

科学技術振興機構 イノベーション拠点推進部

OPERAグループ

伊藤 哲也

| Tel: | 03-6272-3816 |

|---|---|

| E-mail: | opera@jst.go.jp |

東北大学材料科学高等研究所(WPI-AIMR) 広報戦略室

| Tel: | 022-217-6146 |

|---|---|

| E-mail: | aimr-outreach@grp.tohoku.ac.jp |

科学技術振興機構 広報課

| Tel: | 03-5214-8404 |

|---|---|

| E-mail: | jstkoho@jst.go.jp |